Taiwan Semiconductor 2nm, quietly in mass production

台積電已開始量產其 N2(2nm 級)工藝的芯片,儘管未發佈正式新聞稿。N2 工藝採用第一代納米片晶體管技術,預計在性能和功耗方面實現 10%-15% 的性能提升和 25%-30% 的功耗降低。該技術將成為半導體行業最先進的技術,進一步鞏固台積電的技術領先地位。

台積電悄然宣佈已開始量產採用其 N2(2nm 級)工藝的芯片。該公司並未發佈正式新聞稿宣佈量產啓動,但此前曾多次表示 N2 工藝有望在第四季度實現量產,因此該計劃已達成。

台積電在其 2nm 技術網頁上發表聲明稱:“台積電的 2nm (N2) 技術已按計劃於 2025 年第四季度開始量產。 ”

N2 工藝採用第一代納米片晶體管技術,在性能和功耗方面實現了全節點提升。台積電還開發了低電阻重分佈層(RDL)和超高性能金屬 - 絕緣體 - 金屬(MiM)電容器,以進一步提升性能。

台積電 N2 技術在密度和能效方面都將成為半導體行業最先進的技術。憑藉領先的納米片晶體管結構,N2 技術將帶來全節點性能和功耗優勢,以滿足日益增長的節能計算需求。通過我們持續改進的戰略,N2 及其衍生技術將進一步鞏固台積電的技術領先地位,並使其在未來很長一段時間內保持領先地位。”

從性能提升的角度來看,N2 的設計目標是在相同功耗下實現 10%–15% 的性能提升,在相同性能下降低 25%–30% 的功耗,並且對於包含邏輯、模擬和 SRAM 的混合設計,晶體管密度比 N3E 提高 15%。對於純邏輯設計,晶體管密度比 N3E 高出 20%。

台積電的 N2 工藝是該公司首個採用環柵納米片晶體管(GAA)的工藝節點。在這種晶體管中,柵極完全環繞由水平堆疊納米片構成的溝道。這種幾何結構改善了靜電控制,降低了漏電,並能夠在不犧牲性能或能效的前提下實現更小的晶體管尺寸,最終提高了晶體管密度。此外,N2 工藝還在電源傳輸網絡中加入了超高性能金屬 - 絕緣體 - 金屬(SHPMIM)電容器。這些電容器的電容密度是上一代 SHDMIM 設計的兩倍以上,並將薄層電阻(Rs)和過孔電阻(Rc)降低了 50%,從而提高了電源穩定性、性能和整體能效。

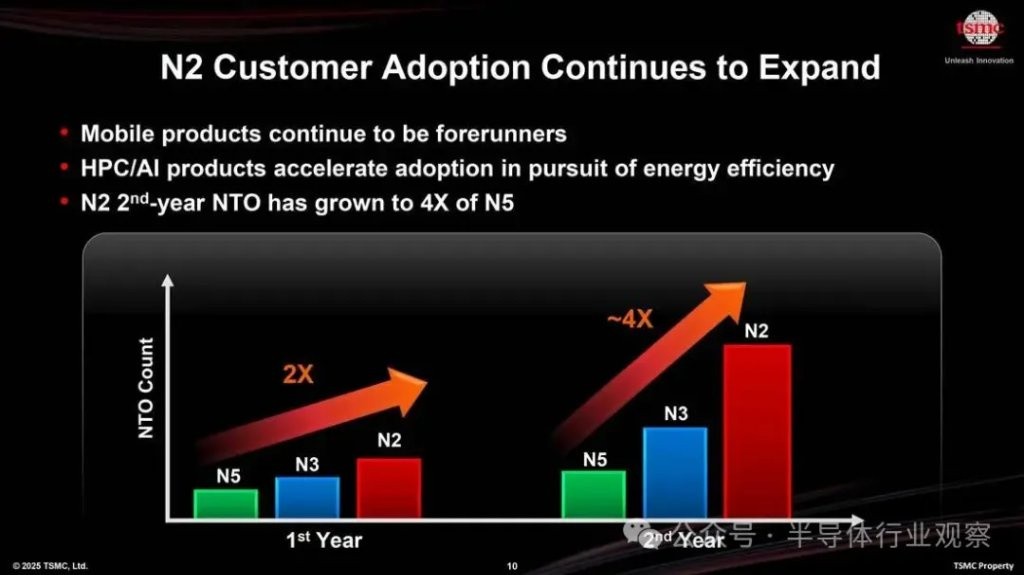

台積電首席執行官魏哲家在 10 月份的公司財報電話會議上表示:“N2 芯片的量產進展順利,有望在本季度晚些時候實現,良率良好。我們預計,在智能手機和高性能計算人工智能應用的推動下,2026 年產能爬坡速度將加快。”

有趣的是,台積電已開始在其位於台灣高雄附近的 Fab 22 工廠生產 2 納米級芯片。此前,市場預期台積電會在 Fab 20 工廠(位於台灣新竹附近)開始提升 N2 工藝芯片的產能,該工廠毗鄰其新的全球研發中心,N2 系列製程技術正是在該中心研發的。Fab 20 工廠的量產可能會稍晚一些。

台積電將在全新的晶圓廠大規模量產 N2 工藝芯片,這始終存在一定的挑戰性。值得注意的是,該公司將在新晶圓廠同時量產智能手機以及更大型的 “人工智能” 和 “高性能計算” 芯片(需要注意的是,高性能計算是一個寬泛的概念,涵蓋了從遊戲主機 SoC 到高性能服務器 CPU 等各種應用),這將增加一些額外的複雜性。通常情況下,台積電會優先量產移動和小型消費級芯片。

同時啓動兩座具備 N2 工藝能力的晶圓廠建設,是因為台積電的眾多合作伙伴對這項新工藝技術表現出濃厚的興趣,因此需要為所有合作伙伴提供充足的產能。此外,從 2026 年底開始,這兩座晶圓廠將用於生產基於 N2P(N2 工藝的性能增強版)和 A16(N2P 工藝的升級版,採用 Super Power Rail 背面供電設計,專為複雜的 AI 和 HPC 處理器打造)的芯片。

魏補充道:“秉承持續改進的戰略,我們將推出 N2P,作為 N2 系列產品的延伸。N2P 在 N2 的基礎上進一步提升了性能和功耗,計劃於 2026 年下半年量產。此外,我們還推出了 A16,它採用了我們一流的超強電源軌(SPR)。A16 最適合具有複雜信號路徑和密集供電網絡的特定高性能計算(HPC)產品。A16 的量產也正按計劃進行,將於 2026 年下半年投產。”

風險提示及免責條款

市場有風險,投資需謹慎。本文不構成個人投資建議,也未考慮到個別用户特殊的投資目標、財務狀況或需要。用户應考慮本文中的任何意見、觀點或結論是否符合其特定狀況。據此投資,責任自負。